# Towards attack-tolerant trusted execution environments

Secure remote attestation in the presence of side channels

**Max Crone**

#### **MASTER'S THESIS** 2021

# Towards attack-tolerant trusted execution environments

Secure remote attestation in the presence of side channels

#### **Max Crone**

Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Technology.

Espoo, 12 July 2021

Supervisors: Prof. N. Asokan

Prof. Panagiotis Papadimitratos

Advisors: Dr. Hans Liljestrand

Dr. Lachlan Gunn

Aalto University School of Science

KTH Royal Institute of Technology School of Electrical Engineering and Computer Science

Master's Programme in Security and Cloud Computing

#### **Abstract**

#### Aalto University, P.O. Box 11000, FI-00076 Aalto www.aalto.fi

| Author                                                                               |                                     |

|--------------------------------------------------------------------------------------|-------------------------------------|

| Max Crone                                                                            |                                     |

| Title Towards attack-tolerant trusted execution environments: Secure reside channels | mote attestation in the presence of |

| School School of Science                                                             |                                     |

| Master's programme Security and Cloud Computing                                      |                                     |

| Major Security and Cloud Computing                                                   | Code SCI3113                        |

| Supervisors Prof. N. Asokan, Prof. Panagiotis Papadimitratos                         |                                     |

| Advisors Dr. Hans Liljestrand, Dr. Lachlan Gunn                                      |                                     |

| Level Master's thesis Date 12 July 2021 Pages 64                                     | Language English                    |

#### **Abstract**

In recent years, trusted execution environments (TEEs) have seen increasing deployment in computing devices to protect security-critical software from run-time attacks and provide isolation from an untrustworthy operating system (OS). A trusted party verifies the software that runs in a TEE using remote attestation procedures. However, the publication of transient execution attacks such as Spectre and Meltdown revealed fundamental weaknesses in many TEE architectures, including Intel Software Guard Exentsions (SGX) and Arm TrustZone. These attacks can extract cryptographic secrets, thereby compromising the integrity of the remote attestation procedure.

In this work, we design and develop a TEE architecture that provides remote attestation integrity protection even when confidentiality of the TEE is compromised. We use the formally verified seL4 microkernel to build the TEE, which ensures strong isolation and integrity. We offload cryptographic operations to a secure co-processor that does not share any vulnerable microarchitectural hardware units with the main processor, to protect against transient execution attacks. Our design guarantees integrity of the remote attestation procedure. It can be extended to leverage co-processors from Google and Apple, for wide-scale deployment on mobile devices.

**Preface**

This thesis work has been conducted as a conclusion to the Erasmus Mundus Master's

degree programme in Security and Cloud Computing (SECCLO). I am most grateful

for the time I have been able to spend with my SECCLO friends while learning,

laughing, eating, and talking. Those moments have taught me more than I had ever

envisioned, and I will carry all of you forth in my mind and in my stories.

I want to thank my supervisor **Prof. N. Asokan** from Aalto University for his guidance

throughout my research. I am additionally very grateful for the amazing discussions I

have had with my advisor **Dr. Hans Liljestrand** from University of Waterloo. There is

much I have come to learn and appreciate on a more fundamental level because of the

motivation and insight from Hans. Furthermore, I would like to thank my supervisor

Prof. Panagiotis Papadimitratos from KTH and my second advisor Dr. Lachlan

Gunn from Aalto University.

Many more people made my time with the Secure Systems Group at Aalto University

one of fond memories. For the sake of brevity, my warmest thanks to Niina Idänheimo,

our collective and loving "mom".

During the work that lead to this thesis, I was supported by scholarships from the

Helsinki-Aalto Institute for Cybersecurity (HAIC). This financial support is gratefully

acknowledged.

A special thanks to my friends Felix Maurer, for our endless discussions and explo-

rations, and Jack Henschel, for all our outdoor gym sessions, sauna evenings, and the

many adventures.

I thank my parents, Ton and Ellen, for their love, encouragement, and support. And

my brother, **Thijs**, for the sense of life we developed together.

Espoo, July 6, 2021,

Max Crone

iii

# **Contents**

| Ab  | stract   |                        |                                        | ii  |

|-----|----------|------------------------|----------------------------------------|-----|

| Pre | eface    |                        |                                        | iii |

| Co  | ntents   |                        |                                        | iv  |

| Lis | t of Fig | gures                  |                                        | vi  |

| Lis | t of Ab  | breviatio              | ens                                    | vii |

| 1.  | Intro    | duction                |                                        | 1   |

|     | 1.1      | Breakin                | ng security                            | 2   |

|     | 1.2      | Trusted                | execution                              | 2   |

|     | 1.3      | Contrib                | outions                                | 3   |

|     | 1.4      | Structui               | re of the thesis                       | 3   |

| 2.  | Back     | ground                 |                                        | 4   |

|     | 2.1      | Trusted                | execution environments                 | 4   |

|     |          | 2.1.1                  | Security requirements and capabilities | 5   |

|     |          | 2.1.2                  | General architecture                   | 6   |

|     |          | 2.1.3                  | Real-world architectures               | 7   |

|     | 2.2      | Side-channel attacks   |                                        |     |

|     |          | 2.2.1                  | Background on microarchitecture        | 11  |

|     |          | 2.2.2                  | Cache-based side-channel attacks       | 14  |

|     |          | 2.2.3                  | Transient execution attacks            | 15  |

|     | 2.3      | .3 seL4 microkernel    |                                        |     |

|     |          | 2.3.1                  | Capabilities                           | 19  |

|     |          | 2.3.2                  | Kernel objects                         | 19  |

|     |          | 2.3.3                  | Memory allocation                      | 20  |

|     |          | 2.3.4                  | CAmkES and capDL                       | 20  |

| 3.  | Probl    | lem state              | ment                                   | 24  |

|     | 3.1      | System                 | model                                  | 24  |

|     | 3.2      | Adversary model        |                                        |     |

|     | 3.3      | Goals and requirements |                                        |     |

| 4.                    | Design     | 1        |                                                     | 27 |  |

|-----------------------|------------|----------|-----------------------------------------------------|----|--|

|                       | 4.1        | High-lev | vel system design overview                          | 27 |  |

| 4.2 Trusted OS design |            |          |                                                     | 28 |  |

|                       |            | 4.2.1    | Dynamic loading                                     | 29 |  |

|                       | 4.3        | Secure c | co-processor                                        | 31 |  |

|                       | 4.4        | Remote   | attestation protocol                                | 31 |  |

| 5.                    | Imple      | mentatio | n                                                   | 33 |  |

|                       | 5.1        | Trusted  | os                                                  | 33 |  |

|                       |            | 5.1.1    | Execution environment and build process             | 33 |  |

|                       |            | 5.1.2    | TEE management components                           | 34 |  |

|                       |            | 5.1.3    | Trusted applications                                | 36 |  |

|                       |            | 5.1.4    | Attestation measurement                             | 37 |  |

|                       | 5.2        | Co-proc  | essor                                               | 42 |  |

|                       | 5.3        | Commu    | nication protocol                                   | 42 |  |

|                       | 5.4        | Dynami   | c loading of ELF files                              | 43 |  |

| 6.                    | Evalua     | ation    |                                                     | 44 |  |

|                       | 6.1        | Security | analysis                                            | 44 |  |

|                       |            | 6.1.1    | Secure remote attestation (S-1)                     | 44 |  |

|                       |            | 6.1.2    | Isolation and integrity of the TEE and TAs (S-2) $$ | 45 |  |

|                       |            | 6.1.3    | Secure dynamic loading (S-3)                        | 47 |  |

|                       | 6.2        | Perform  | ance considerations                                 | 47 |  |

| 7.                    | Discus     | ssion    |                                                     | 49 |  |

| 8.                    | Relate     | ed work  |                                                     | 50 |  |

| 9.                    | Concl      | usion    |                                                     | 52 |  |

| Ref                   | References |          |                                                     |    |  |

# **List of Figures**

| 2.1 | General TEE software architecture                   | 7  |

|-----|-----------------------------------------------------|----|

| 2.2 | Memory to cache mapping                             | 14 |

| 2.3 | Example seL4 system                                 | 21 |

| 2.4 | Objects section of a capDL specification            | 22 |

| 2.5 | Capabilities section of a capDL specification       | 23 |

| 3.1 | Simplified system overview                          | 25 |

| 4.1 | High-level system overview                          | 28 |

| 4.2 | Trusted operating system overview                   | 30 |

| 4.3 | Remote attestation flow in system design            | 32 |

| 5.1 | System overview of trusted OS implementation        | 34 |

| 5.2 | Driver component state diagram                      | 36 |

| 5.3 | Type-length-value encoding scheme                   | 43 |

| 6.1 | Graphical security analysis of the attestation flow | 46 |

# **List of Abbreviations**

ADL architecture description language.

**API** application programming interface. BTB branch target buffer. capDL capability description language. **CNode** capability node. **CSpace** capability space. **DRM** digital rights management. EL exception level. ELF executable and linkable format. **EPC** enclave page cache. **HSM** hardware security module. **IPC** inter-process communication. **ISA** instruction set architecture. LLC last-level cache. LVI load value injection. MAC message authentication code. MEE memory encryption engine. NS non-secure. **OEM** original equipment manufacturer. **OS** operating system. PD page directory.

PHT pattern history table.

PKI public key infrastructure.

**PoC** proof-of-concept.

**PSP** platform security processor.

PT page table.

**REE** rich execution environment.

ROB re-order buffer.

**RoT** root of trust.

**RPC** remote procedure call.

RSB return stack buffer.

SCR secure configuration register.

**SECS** SGX enclave control structure.

SGX Software Guard Exentsions.

**SMC** secure monitor call.

SoC system on chip.

STL store to load.

TA trusted application.

TCB trusted computing base.

TEE trusted execution environment.

TLV tag-length-value.

**TPM** trusted platform module.

VSpace virtual address space.

## 1. Introduction

"Nobody ever figures out what life is all about, and it doesn't matter. Explore the world. Nearly everything is really interesting if you go into it deeply enough"

Richard P. Feynman

The development of the Internet and its increasing presence in society have spurred demand for computer systems. Computers are now found everywhere, from large scale industrial data centers, to tiny applications in embedded environments, and mobile devices everyone carries. With the increased reliance on computing devices has also come an increase in requirements for their security.

Already since the 1960's, there have been efforts to secure computer operating system (OS) against criminal actors [44]. Early work on security and standards mostly came from governmental organizations in the United States [22], including the Department of Defense (DoD) and the Air Force Electronic Systems Division. The resource-sharing computer systems of that time relied on separation enforced by the OS. Generally, these systems were found to provide practically no protection from deliberate attempts to violate the OS [22]. As a reaction, James Anderson and others introduced the concept of a reference monitor in a technical report from the 1970's [4], kicking off the serious attention to systems security in the IT sector. The developments of these times are captured in the proliferation of general security principles still applied to OSs today.

OS security in this thesis encompasses three principles: integrity, isolation, and access control.

The first principle is the *integrity* of computer programs and data stored in memory and other media, i.e., the bits that encode them stay consistent over time with high reliability. Violations of integrity, either malicious or unintentional, can cause significant problems. For example, the disfunction of software crucial for proper operation of a modern car might lead to a disaster. As another example, violations of data integrity in global financial systems can severely impact the life of real people.

The nature of the early multi-user systems and the concurrent operation of modern computers give rise to the second security principle; *isolation*. Even though an OS might be executing many different processes concurrently, none should be able to interfere with each other in an unauthorized manner. To securely run software, processes

must be isolated and prevented from affecting each other's memory and execution, except through well-defined and intended interfaces.

Then there is the security principle of *access control*. The OS is tasked with separating the data and other resources owned by different programs or users. It must only allow access to data for the entity that owns it, or for others who have been assigned appropriate rights. Access control is thus a method of providing confidentiality of resources.

Though the security principles are clear, in practice it has proven to be challenging to ensure complete adherence to them. OSs and other computer programs are so complex that formal verification of security properties never seemed feasible. Over time, security issues have become more relevant and of higher impact.

#### 1.1 Breaking security

Memory safety bugs are prevalent and form one of the most dangerous types of software vulnerabilities [80]. Any such vulnerability is a potential information leak. They are found — among other places — in web browsers such as Chrome and Firefox, and cryptographic libraries protecting internet connections [80, 25]. The consequences of these bugs extend to the compromise of secret keys that protect passwords, banking details, and personal information sent over the internet.

Other run-time attacks exploit software defects to influence a targeted computer system into behaving maliciously instead of only leaking information. These might ultimately give the attacker access to the computer system. A famous example is the Morris worm [66], which exploited a software defect to spread itself to a large share of the computers connected to the Internet.

A different class of attacks are *side-channel* attacks. Side-channel attacks exploit information retrieved from computer system components functioning as intended, such as timing information [14, 32], power consumption [49, 82], and electromagnetic leaks [2]. These attacks often aim to retrieve cryptographic keys or other secrets, that would allow access to confidential data [14] or enable impersonation [34].

#### 1.2 Trusted execution

Due to the prevalance of security vulnerabilities, researchers and programmers have sought solutions to protect security-critical software against attacks. One idea is to separate sensitive software and data from the OS. Compromised applications or even an adversary controlling the OS can then no longer access the sensitive software. This is

the premise of a trusted execution environment (TEE). A TEE isolates the execution of confidential programs and operations on sensitive data from a potentially malicious OS. It does this through a combination of software and hardware mechanisms. Examples of technologies for TEEs are Arm TrustZone [6] and Intel SGX [57].

However, the existing TEE solutions have not been infallible either. Researchers identified more than a hundred vulnerabilities in TrustZone-assisted TEE systems in recent years [17]. There are more than twenty published attacks on Intel SGX [61], some of which manage to compromise the full memory contents of the SGX system. Many of these are side-channel attacks that compromise the secure keys used for attestation in these systems. This consequently breaks the trust in the software running in these TEEs.

#### 1.3 Contributions

We present an architecture for TEE remote attestation that upholds integrity guarantees in the presence of the same attacks that compromised earlier TEE technologies. We achieve this by leveraging the formally verified seL4 microkernel and a secure coprocessor for cryptographic operations. The following lists our contributions.

- Designed and implemented a TEE remote attestation architecture with strong integrity and isolation security guarantees in the presence of vulnerabilities and side-channel attacks.

- Designed a method to dynamically load and execute user-provided trusted applications (TAs) in our TEE.

- Considered the performance overhead of our TEE remote attestation architecture.

#### 1.4 Structure of the thesis

The remainder of this thesis is structured as follows. Chapter 2 presents a background on TEEs, side-channel attacks, and the seL4 microkernel. Chapter 3 formulates the system and adversary model and makes the security goals and performance goals of this work explicit. Chapter 4 describes our proposed TEE remote attestation system design. Chapter 5 explains how we implemented our TEE remote attestation system. In Chapter 6, we evaluate our system's implementation from a security perspective and consider its performance properties. Chapter 7 discusses what we would have done differently given more resources and describes future work. In Chapter 8, we describe the related work with respect to TEE designs and defenses. Finally, Chapter 9 concludes this thesis work.

# 2. Background

"Let's start with the end of the world, why don't we? Get it over with and move on to more interesting things."

N.K. Jemisin, The Fifth Season

#### 2.1 Trusted execution environments

A trusted execution environment (TEE) is an environment that enforces that code and data loaded inside cannot be tampered with or read by code outside that environment. TEEs provide isolation for small pieces of trusted software from the rest of the device, called the rich execution environment (REE), which typically includes an operating system (OS), such as Linux, and user space applications. To enforce this isolation, TEEs use hardware-based security mechanisms in combination with software security mechanisms. This allows developers to design applications that remain secure even when the REE OS is compromised.

Trusted platform modules (TPMs) and hardware security modules (HSMs) are two examples of TEEs. A TPM generally provides a secure key storage for hard drive encryption and a minimal set of cryptographic operations often used for validating steps in the booting processing. An HSM typically provides hardware-accelerated cryptographic operations and secure key and certificate storage. Both are often implemented as separate hardware microcontrollers, embedded at different levels of a system. In this work, we are concerned with a TEE that provides an isolated execution environment on the main processor, where sensitive data is stored, processed, and protected. Specifically, by running it on the main processor it takes advantage of higher processing speed and larger amounts of memory than other secure environments — i.e., TPMs and HSMs.

There are multiple use cases for TEEs [26, 68].

Digital rights management (DRM) solutions might make use of a TEE, when distributors of media content (e.g., films, music) want to protect their digitally encoded content from being copied by the owner of the device. For example, a TEE decrypts an incoming media stream and pushes it over a trusted path to an approved display. Or, a TEE prevents other applications on the device from reading the copyright-protected contents when they are stored on the device. It does this by only exposing the content

to environments approved by the distributor or developer. As an example, Widevine is a content protection system by Google that specifies the use of a TEE [93].

A TEE is also suitable for digital payment scenarios that require high security and trust in the device. It helps to provide strong identification and proof of transaction. The TEE secures the execution of cryptographic algorithms used for signature verification and authentication.

Many devices today secure their biometric authentication methods with a TEE, e.g., Apple's and Samsung's mobile devices [5, 85]. The TEE stores a template for the biometric factor — face, or fingerprint — and performs extraction and matching of new samples in a secure manner. They often incorporate trusted hardware paths for input, to minimize the opportunities for attackers to gather data or exploit the user via malicious user-interface elements.

In the scenario of cloud computing, a tenant can use TEEs to store sensitive data such as customer details or to perform sensitive computations, while preventing the cloud provider from accessing the data. This provides better data security for the tenant and reduced liability for the cloud provider.

#### 2.1.1 Security requirements and capabilities

The GlobalPlatform industry consortium defines a set of high level security requirements for TEEs in their standard on TEE system architecture [84]. We summarize those requirements here.

- Protect assets from the REE and other (execution) environments, through hardware mechanisms that other environments cannot control.

- Prevent system components from accessing assets in a TEE unless they themselves are a protected asset of the TEE.

- Protect against some physical attacks [83].

- Instantiate the trusted OS from a root of trust (RoT) through a secure boot process.

- Provide trusted storage of data and keys.

- Enforce that software outside the TEE can only call the external application programming interface (API) of the TEE, that can verify the acceptability of an operation. Prevent outside software from directly calling functionality from any of the TEE's internal APIs.

To prevent hardware simulation, a TEE uses a hardware RoT — a highly reliable, secure-by-design component that performs specific, security-critical functions. The root of trust consists of a set of private keys that are provisioned to the device during

manufacturing, in a manner that prevents them from being changed. Manufacturers store the respective public keys, together with information from trusted parties (i.e., chip vendors). Chip vendors use this key infrastructure to, for example, sign and distribute trusted firmware.

Generally, we consider an environment to be a TEE when it has three main capabilities.

- 1. **Isolation** of execution from the REE, providing confidentiality and integrity for code and data.

- 2. **Secure storage** of persistent data, guaranteeing confidentiality and integrity across reboots in the presence of an adversarial REE.

- 3. **Attestation** of the software running in the TEE; attesting to a third party that a certain version of the application is loaded or executing in the TEE.

#### Remote attestation

Remote attestation is a process of verifying the integrity of a remote system's state. This generally happens via a challenge-response protocol, where the relying third party poses a fresh challenge that the remote system responds to with a verifiable cryptographic signature.

The remote system additionally includes an attestation of the software on the system. An attestation is a cryptographic signature that certifies a hash of the software's state. Though there exist control-flow attestation mechanisms that take place later in the execution lifecycle of a software application [1], in this work, we take attestation to mean the verification of the initial state of an application. This is called static attestation.

Remote attestation requires a trust assumption for authenticity of the attestation report. The platform of the remote system thus generally contains a RoT that forms the basis of a remote relying party's trust in a system and, consequently, their trust in the remote attestation procedure. The relying party can verify an attestation report against an endorsement certificate created by the trusted hardware's manufacturer.

#### 2.1.2 General architecture

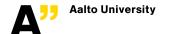

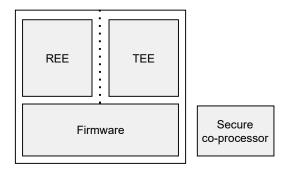

The GlobalPlatform industry consortium specifies a software architecture for TEEs that outlines the relationship between major components. Figure 2.1 depicts a simplified architecture based on GlobalPlatform standards [84].

The trusted applications (TAs) in a TEE generally do not run complete user-facing applications. Instead, normal applications in the REE invoke them via client applications to perform specific tasks that require the security guarantees provided by the TEE. For

**Figure 2.1.** General trusted execution environment (TEE) software architecture. The TEE and rich execution environment (REE) are isolated by hardware mechanisms, but can still communicate via the platform application programming interface (API). The TEE runs its separate, trusted operating system (OS), and exposes internal APIs to provide functionality to every trusted application (TA) it runs.

example, a banking application might only call a TA to handle user authentication when an individual starts a transaction. The REE application can manage the rest of the transaction process that does not require those higher levels of security.

#### 2.1.3 Real-world architectures

There exist several hardware technologies that support the implementation of TEEs. Arm designed TrustZone as extension to a selection of their architectures, which they license to other companies. Microprocessor manufacturers AMD and Intel developed platform security processor (PSP) and Software Guard Exentsions (SGX) respectively. For RISC-V, there are multiple TEE designs available [58, 54, 29]

Intel SGX and Arm TrustZone are the most widely used in TEE implementations today.

#### Arm TrustZone

Arm TrustZone is a set of security extensions to the Arm architecture [69]. TrustZone adds processor support for a new execution mode and memory protections that allow

the system to distinguish between two protection domains called secure world and non-secure world. Both worlds are hardware-isolated and have different sets of privileges, with non-secure software prevented from accessing any resources from the secure world. At any point in time, the processor operates exclusively in one of the two worlds.

The current world in which the processor executes is encoded in a new processor bit called the non-secure (NS) bit, which can be read from the secure configuration register (SCR). TrustZone introduces the monitor mode which is responsible for preserving the processor state when world switches occur. Via a new privileged instruction called the secure monitor call (SMC), software stacks in both worlds can be bridged by the secure monitor software. TrustZone also provides memory extensions to configure memory regions as secure or non-secure, to protect non-secure world applications from accessing memory belonging to the secure world.

The Arm architecture has different levels of access to system and processor resources called exception levels (ELs) [8]. The common usage model of ELs is as follows.

- EL0 for applications

- EL1 for the OS kernel

- EL2 for hypervisors

- EL3 for the secure monitor

The secure monitor that handles the world switches operates on EL3, which is the highest privilege level. It has thus access to more system and processor resources than any OS, which allows it to effectively isolate the OS in the non-secure world from the OS in the secure world.

This described the TrustZone extensions for Arm's application processors (Cortex-A). The TrustZone requirements for Arm microcontrollers (Cortex-M) [7] are different, because of the processor family's focus on fast context switches and low-power applications. TrustZone for Armv8-M uses a memory-map based division between worlds where transitions take place in exception handling code. This allows it to remove the monitor mode and thus the need for any secure monitor software, leading to more efficient world transitions.

TrustZone is not a TEE in itself yet. Instead, its secure world provides the execution environment where a TEE may reside. Examples of TEEs implemented on top of TrustZone technology are Samsung Knox [70] and Open-TEE [56].

During boot, a TrustZone-enabled Arm processor enters the secure world to allow privileged software to initialize their protections and perform hardware measurement operations. This feature enables the implementation of a secure boot process that veri-

fies the platform state, which forms the basis for trusted remote attestation. For example, Samsung Knox provides secure boot using TrustZone in this manner [69].

#### Intel SGX

Intel SGX differs from TrustZone in the size of its trusted computing base (TCB). As a general rationale, a smaller TCB has a smaller attack surface and thus a lower chance of vulnerabilities, leading to better security. The split-world architecture of TrustZone means that any software operating at the higher privilege level is inherently part of the TCB, because they have greater access to the machine. In contrast, SGX uses an *enclave* architecture, backed by trusted hardware, that provides strong isolation between TAs, such that a trusted OS does not become part of the TCB.

Enclaves are execution environments for code and data that are protected from any outside software environment. The threat model for enclaves only trusts the enclave itself and treats all outside processes — including the OS and any hypervisor — as potential adversaries.

An SGX enclave is part of the host process application. However, an application is not able to access an enclave's memory, which resides in the enclave page cache (EPC). The EPC is a protected area of memory consisting of 4 KB pages that stores enclave code and data. This memory area is encrypted using a new hardware unit called the memory encryption engine (MEE), and is only decrypted once inside the physical processing core [37].

An application creates and initializes enclaves for its own use. SGX associates every enclave with an SGX enclave control structure (SECS) that stores metadata in a dedicated EPC page. The initialization of an SECS creates a new enclave. An application then loads the initial code and data into the enclave. For every page loaded, the system software updates the enclave's measurement that is used for attestation. Measurements are cryptographic hashes that uniquely identify a system state. An application initializes its enclave via Intel's architectural *Launch Enclave*. It can then enter the enclave by transferring control to a pre-determined location within it.

SGX supports two types of attestation: local and remote [3, 45]. In local attestation, an enclave proves its identity to another target enclave on the same system. It produces a signed attestation report that contains a hash of the measured contents of the enclave (MRENCLAVE), its sealing identity (MRSIGNER), its attributes, and additional information. It also appends a message authentication code (MAC) created with a symmetric key unique to the platform. The target enclave verifies this report to establish confidence that it is communicating with a legitimate enclave on the system.

Where local attestation uses a symmetric key for verification, remote attestation to

outside the platform requires asymmetric cryptography. SGX provides an architectural enclave specifically for remote attestation; the *Quoting Enclave*. The Quoting Enclave verifies reports from other enclaves on the system following the method described above. It then replaces the MAC with an attestation signature produced with the Attestation Key. The Attestation Key is generated by the Provisioning Enclave in SGX and Intel's provisioning service when a new enclave is created. The Quoting Enclave uses this key to generate attestations — called *quotes* — that can be verified to originate from a legitimate SGX enclave hosted on trusted hardware. It additionally includes the hashed measurements of the contents of the enclave. Finally, the remote party verifies that this value agrees with what they expected; ensuring that a specific piece of software is running.

The provisioning enclave is part of the trust chain on which attestation builds. During manufacturing, Intel generates a provisioning secret for a processor. Every processor additionally has secrets sealed into its e-fuses — a form of one-time programmable read-only memory. The provisioning enclave uses both elements to demonstrate the SGX platform's authenticity to Intel, in order to receive appropriate attestation keys. This ensures the trust in the later remote attestation phases.

#### 2.2 Side-channel attacks

Side-channel attacks are a type of security exploit. Many classes of security exploits target specific vulnerabilites in software. Vulnerabilities such as memory safety violations, input validation errors, and race conditions are often caused by mistakes or inaccuracies from the people developing the software. In contrast, side-channel attacks are based on information gained from legitimate operation of computer systems. However, no one had expected this information could also be used to infer valuable data; it is thus accidental leakage of sensitive data. Originally, side-channels were understood to be the exploitation of physical phenomena that were the by-product of the execution of tasks on electronic devices. These original channels include power consumption, electromagnetic radiation, heat, and noise [79]. Researchers have shown how to find secret keys by analyzing power consumption [49], how to break power analysis countermeasures and extract compromising information via electromagnetic radiation [2], and how to extract RSA keys using acoustic cryptanalysis [34]. Timing attacks are another side-channel attack. They enable an attacker to infer secret information based on the time it takes a computer to perform certain tasks [14]. Timing attacks often target cryptographic operations to extract secret keys.

TEEs are also vulnerable to these side-channels. In 2017, a TEE based on TrustZone

was found to be vulnerable to a timing attack that enabled attackers to extract cryptographic secrets [17]. The CLKscrew attack exploits energy management mechanisms to extract secret cryptographic keys from TrustZone and escalate its privileges by loading self-signed code [82]. Plundervolt is a similar attack, but it targets Intel SGX instead of TrustZone [59].

These side-channel attacks are distinct from earlier computer security problems. As such, they also require different mitigations in comparison with the usual software vulnerabilities. These mitigations range from signal size reduction, time randomization, to the introduction of noise to decrease the amount of information that is leaked, and constant-time operations [79].

In the remainder of this section we describe the class of side-channels that appears most frequently in attacks against TEEs: microarchitectural side-channels. In particular, we consider cache side-channel attacks and transient execution attacks. These side-channel attacks exploit complex microarchitectural behavior used to improve processor performance.

#### 2.2.1 Background on microarchitecture

A microarchitecture is the implementation of an instruction set architecture (ISA) in a processor. The ISA serves as an interface between hardware and software. As such, it abstracts over details concerning functional implementation, such as pipelines and caches. These constitute the microarchitecture instead. Examples of ISAs are the ubiquitous x86 architecture [9], Armv8 [8], and more recently RISC-V [92]. Examples of microarchitectures on the other hand, are Intel's Cypress Cove implemented on the eleventh generation Intel Core desktop microprocessors [42], and Arm's Cortex-A78 implemented in several Samsung Exynos [28] and Qualcomm Snapdragon microprocessors [30], among others. Both the architecture and microarchitecture are stateful. The architectural state includes memory and registers that are accessible to the programmer. Whereas the microarchitectural state includes entries in various caches that are used to improve performance without affecting the architectural state.

#### Instruction cycles and pipelining

The instruction cycle is an important concept of microarchitectures. By repeating the instruction cycle, the processor runs programs. On a high level, the instruction cycle consists of four steps.

- 1. Fetch and decode an instruction

- 2. Retrieve data needed for the instruction

- 3. Execute the instruction

- 4. Write the results to the destination register

A great improvement to performance of the cycle is the concept of instruction pipelining. Early processors would execute all four steps sequentially for a single instruction before they moved on to the next instruction. This approach is inefficient. While executing an instruction, the decoding circuitry of the processor is idle. In fact, with this sequential approach, large parts of the processor circuitry will be idle most of the time. It would instead be much more efficient to already decode the next instruction while processing the current one. This is exactly the idea of instruction pipelining. In order to keep every part of the processor busy, incoming instructions flow through the processor in multiple stages. Thus at any clock cycle, there can be multiple instructions in the pipeline. The aim is to keep every part of the processor busy. Modern pipelines consist of fourteen to twenty stages. Embedded processors might do with less; between six and twelve. Putting significantly more stages in the pipeline eventually hits the law of diminishing return. This is exemplified by Intel's Prescott microarchitecture that had a deeper instruction pipeline of 31 stages, but experienced issues with power consumption and heat dissipation [43].

There are several more techniques for optimizing instruction pipelines. However, these optimizations also introduce new vulnerabilities such as side channels, e.g., when instructions alter the cache state in a way that leaks sensitive data. Such vulnerabilities are hard to mitigate, because programmers cannot directly control the microarchitectural state, and the microarchitectural behavior is often complex, propriety, and undocumented.

#### Out-of-order execution

Processors optimize their utilization by allowing for *out-of-order* execution of instructions in the pipeline. For example, performing a memory operation takes a relatively long time and if the processor were only executing instructions in-order, it would have to wait until the memory operation returned. Instead, the processor might already execute the next instruction *out-of-order* while it is waiting. This speeds up general execution of programs.

A processor stores instructions it completed out-of-order in a buffer. When the execution flow catches up, the processor retrieves the instructions from the buffer in the correct order. Only then do the results of these instructions become visible in the architectural state.

#### *Speculative execution*

When performing out-of-order executions, a processor often does not know the future instruction sequence yet. For example, this is the case when execution reaches conditional branch instructions whose direction depends on earlier instructions that have not completed yet. Recall the example of a memory operation from earlier. To address

this problem, processors speculate on the value that determines a future instruction sequence. They then speculatively execute instructions along that path. When execution of the speculated instruction is resolved, the processor verifies whether the prediction was correct. Upon a correct prediction, the processor retrieves the speculative instructions' results and applies them in program execution order. Otherwise, the processor abandons pending instructions along the path, restores its state from a checkpoint, and resumes execution along the correct path. The speculative execution technique increases the performance of microprocessors.

#### Branch prediction

Branch prediction is related to the instruction pipelining concept. Imagine that one of the instructions going through the pipeline is a branch instruction. A branch instruction is the implementation of an if-else construct. Depending on the argument value, there will be different instruction sequences that come next. However, when the branch instruction is finally executed, several other instructions will already be in the pipeline. If the instructions in the pipeline are from the incorrect branch, the one that does not end up being followed, the processor wasted cycles on executing them anyway. This is where the *branch predictor* comes into play. Its task is to make the most accurate predictions for which branch is most likely to be taken. This prediction will then inform which instruction sequence flows through the pipeline. The branch predictor bases its guesses on historical information, e.g., which branch has been taken more often recently. It is built as a digital circuit on the processor.

Branch mispredictions have a larger effect on system performance when the instruction pipelines are deeper. Because instructions cannot just be removed from the pipeline, they have to go through all stages up until execution. The number of cycles wasted upon a branch misprediction is thus equal to the number of stages from fetch to execution.

Because the branch predictor acts on historical information, it can also be intentionally *trained* to behave in a specific way. A malicious actor could use this to either infer what computations have altered its behavior, or even to transiently execute an attacker-chosen instruction sequence.

#### Caches

Processor caches are an important part of the memory hierarchy in modern computers [81, 32]. With the speeds of memory and processors diverging over the last decades, caches help to bridge the gap. Caches are fast, but small and expensive, memory that are used to store data being accessed by the processor. Most processors include a hierarchy of cache levels. Today, they often have three levels: from L1, which is fastest and smallest, to L3, which is larger but slower. The L1 cache is frequently split up in

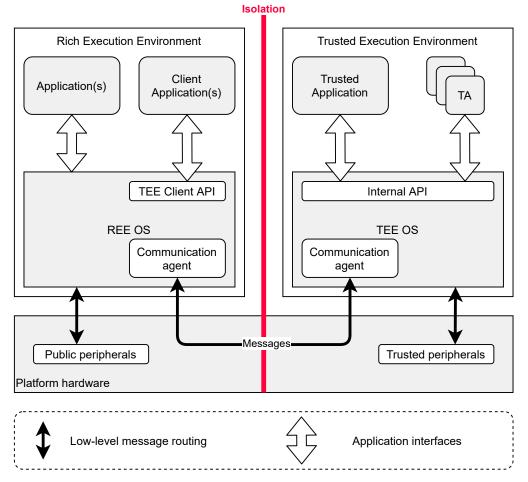

**Figure 2.2.** Typical addressing of a cache line in a 2-way set-associative cache. The memory address determines the exact mapping. It is split up in different *cache fields* that indicate a byte offset, the set index, and the identifying tag (consisting of the remaining most significant bits).

separate caches for instructions and data, called L1i and L1d respectively. The use of caches is more efficient when the *hit rate* is high, i.e., when a higher fraction of requests is satisfied from the cache instead of accessing the slower main memory. A cache miss occurs when the requested data is not found in any of the caches. The processor then fetches the data from main memory and places it in a cache. If there already exists other data in the slot, the processor evicts — i.e., removes — it before storing the new data. A higher share of cache evictions impacts performance negatively.

Caches are divided into *cache lines* [39]. A cache line holds an aligned block of adjacent bytes from memory, usually a power of two in size. Grouping together adjacent bytes makes use of spatial locality and limits implementation complexity. As a consequence, if replacing any single byte in the cache, the whole cache line needs to be evicted.

A cache placement policy determines where the data at a memory address is placed in a cache. Most architectures specify a set-associative policy. A W-way set-associative cache divides its memory into *cache sets* that each consist of W cache lines. Cache sets are directly addressable, but the *way* where the cache line resides must be found by comparing its tag. Figure 2.2 illustrates a typical cache addressing scenario.

#### 2.2.2 Cache-based side-channel attacks

Many cache-based side-channels originate from timing differences measurable by the attacker. The intuition stems from the fundamental purpose of caches; the processor wants to access certain data faster. An attacker can measure memory access times to infer whether the victim has touched the corresponding cache lines. When a measurement takes relatively long (~100ns), the attacker infers that the data had to come from

memory rather than from cache. In contrast, if the request returned quickly (10-25ns), the attacker knows that it hit the cache. This principle allows an attacker to learn about the memory access patterns of the victim. Researchers have proposed several techniques to exploit this.

#### $P_{RIME}+P_{ROBE}$

This technique from 2006 [67] consists of two main steps. Firstly, an attacker *primes* an area of the cache by filling cache sets with its own cache lines. After waiting for the victim to have executed again, the second step encompasses *probing* — accessing and changing data — the cache lines the attacker loaded earlier. By observing the timing of each probe, the attacker sees which cache lines have been evicted. This tells them that the victim must have accessed an address in memory that maps to the same cache set.

#### Flush+Reload

The advantage of Flush+Reload over Prime+Probe is that it allows to target a specific cache line rather than only a cache set [95]. The technique uses the last-level cache (LLC), which is shared by all cores on a processor implementing the x86 architecture, and it relies on the existence of shared virtual memory (e.g., shared libraries).

A FLUSH+RELOAD attack consists of three phases. Firstly, the attacker flushes the targeted line from the cache. Secondly, they wait to allow for the victim to access the memory line. Thirdly, the attacker reloads the memory line and measures the time it takes. If the victim accessed the memory line and caused it to appear in the same cache location again, the reload operation will return quickly. Otherwise, the victim did not access the memory line and the attacker's probe will take longer because the line needs to be fetched from main memory first.

Flush+Reload is a generic technique also used as a building block for more advanced attacks, such as Spectre and Meltdown.

#### 2.2.3 Transient execution attacks

Transient instructions are instructions executed speculatively by the processor, but that are discarded after a pipeline flush, e.g., on a branch misprediction [16]. The pipeline flush discards any architectural effects of these pending instructions. However, transient execution attacks leverage the fact that transient instructions have persisting microarchitectural side effects to exfiltrate data across security boundaries. An attacker can steer or even choose the instruction sequences to execute transiently, depending on the attack they employ.

The field of transient execution attacks emerged recently with the publication of the

Spectre and Meltdown attacks [50, 55]. These attacks have shown how to dump memory, intercept passwords, and reconstruct images. Transient execution attacks are also shown to work against TEEs, e.g., in SgxPectre [19] and Foreshadow [15].

#### Spectre

Spectre attacks trick a victim into speculatively executing instructions which leak confidential data via a covert channel [50]. These attacks consist of two main parts: a microarchitectural element to exploit, and a covert channel through which to exfiltrate data. Canella et al. categorize Spectre variants based on the microarchitectural elements they exploit: pattern history table (PHT), branch target buffer (BTB), return stack buffer (RSB), and store to load (STL) [16]. All of these are part of predictive optimizations in microprocessors. Spectre attacks use cache-based covert channels (Section 2.2.2) to exfiltrate data across architectural security boundaries. The original paper describes attacks using Flush+Reload and a variant called Evict+Reload [50].

Spectre attacks bypass *software-defined* security boundaries such as bounds checking. An attacker can trick the victim into transiently executing instructions on memory locations they have access to, but which the attacker is not authorized to address directly.

To trick the victim into speculative execution of these instructions, an attacker first prepares the processor by mistraining its prediction machinery. The attacker also prepares the covert channel, e.g., by performing the flush portion of the Flush+Reload attack. As a final step in the setup, the attacker performs operations to trigger the desired speculative state. For example, they perform targeted memory reads that cause the processor to evict a specific value from cache that is needed to determine a branch target.

In the second phase, the processor performs the transient execution of instructions. The transient execution may be triggered by requesting the victim to perform an action via a system call, socket, or file. The results of this speculative execution reflect in the prepared microarchitectural side-channel. For example, the victim speculatively reads a memory value at an attacker-chosen address and subsequently performs a memory operation that exposes the value via its modifications to the cache state.

Lastly, the attacker recovers the confidential data by timing the reads of memory addresses for the monitored cache lines, similar to a traditional side-channel attack.

#### Meltdown

Whereas Spectre attacks exploit transient execution following mispredictions of control or data flow, Meltdown exploits transient execution after a faulting instruction [55]. The key observation is that speculation may still occur after exceptions in transient

instructions. This characteristic allows the Meltdown attack to read kernel memory from user space, bypassing architectural isolation barriers.

Meltdown is similar to Spectre and as such consists of the same two abstract parts again. Firstly, Meltdown uses exceptions as the element to cause transient execution. For the second phase, Meltdown uses a cache-based covert channel.

Most Meltdown variants rely on page faults to trigger the transient execution [16]. The original attack reads data from a kernel memory address, which eventually causes a page fault. Because of out-of-order execution, vulnerable processors identify the exception generating instruction, but only tag its entry into the re-order buffer (ROB) with an exception bit. They then continue speculative execution of other instructions. The exception is handled once instructions are retired from the ROB and become visible in the architectural state. By that point, transient instructions encoded the privileged data into the microarchitectural state.

In its second phase, Meltdown uses the Flush+Reload technique to exfiltrate confidential data kernel memory. Transient instructions encode the privileged data by accessing specific cache lines. The attacker recovers this value by measuring the access time for all cache lines.

All major operating systems used to map the kernel address space into the virtual address space of every process. They also mapped physical memory into the kernel address space. As such, an attacker employing Meltdown could read the entire physical memory of a computer system. Since publication of the Meltdown attack, mitigations isolate the kernel page table [35].

#### Extensions targeting Intel SGX

The original Spectre and Meltdown attacks were not demonstrated on Intel SGX. However, later research has shown variants that target Intel SGX. Consequences include the keypair extraction of Intel's architectural enclaves (Section 2.1.3) and the compromise of enclave secrets.

Foreshadow is an extension of Meltdown that targets Intel SGX [15]. It leverages the same processor vulnerability that allows an attacker to use the results of transient unauthorized memory accesses. Meltdown exploits transient execution to access kernel memory before the fault caused by the access violation is handled and Meltdown triggers a race condition by causing a page fault after accessing kernel memory. This enables the exploitation of transient instructions, before the fault handler causes them to revert. Intel SGX applies abort page semantics; silently replacing the read data with a dummy value instead of raising a fault. Thus the race condition that enables Meltdown is absent when targeting Intel SGX. However, Intel SGX only applies the

abort page semantics after a legacy page table permission check succeeds without issuing a page fault. Foreshadow avoids these mechanisms by revoking all access permissions to the targeted enclave page, such that any access will lead to a page fault. This page fault leads to the race condition that enables the transient execution without abort semantics. Foreshadow then retrieves secrets in a similar vain as Meltdown; by measuring the time it takes to access certain cache lines. Furthermore, Foreshadow implements various optimization techniques to increase the bandwidth and reliability of secret extraction.

The SGXPECTRE attack can also extract secrets from Intel's architectural enclaves, but it exploits a different type of hardware vulnerability than Foreshadow [19]. Specifically, it presents ways to inject branch targets into SGX enclaves to trigger transient execution and leak secrets out of the enclave. This technique is similar to the Spectre attacks described earlier.

Lastly, the recent load value injection (LVI) attack presents new exploitations of Intel SGX that are not hindered by mitigations against Spectre and Meltdown [88]. LVI is not limited to hijacking branch outcomes, but allows to replace the result of any victim load micro operation with attacker-controlled data.

#### 2.3 seL4 microkernel

seL4 is a microkernel of the L4 family, designed for applications in safety- and security-critical systems with high assurance and high performance [48].

As a microkernel, seL4 provides only a minimal set of features in kernel space. These features include inter-process communication (IPC), threads, virtual address spaces, capability-based access control, and interrupt control. seL4 leaves the implementation of other OS functionality — e.g., memory management, networking stack, device drivers — up to user space. This approach to kernel design creates a sufficiently small TCB that allows to formally prove its correctness.

As a microkernel, seL4 is unique in that it includes formal and automated proofs that the implementation is functionally correct, and that the formal model ensures confidentiality and integrity [47]. These proofs do not cover protection against timing channels — e.g., timing-based cache side-channels leveraged by Spectre and Meltdown (Section 2.2). However, the researchers behind seL4 are working towards formal proofs of timing-channel prevention [33, 41].

#### 2.3.1 Capabilities

seL4 is a capability-based microkernel [71]. A capability is a reference to an object, which also encodes access rights to that object. For example, a read-write capability to a frame object gives the owner of the capability read and write access to a specific memory frame. Capabilities allow for delegation of access. *Minting* a capability copies it to a new capability that may have fewer rights. It can then be transferred to another entity. Revoking a capability strips the encoded access to the referenced object away from the holder of a capability, and recursively revokes any capabilities that were derived from it. Capabilities are monotonic, i.e., new capabilities will never have more access rights than the capability they are derived from.

An application's capabilities conceptually reside in its capability space (CSpace), which is implemented as a directed graph of capability nodes (CNodes). Every CNode is a table of slots, where each slot may contain other CNodes. In seL4, the kernel manages all capabilities and an application only references these by their addresses.

SeL4 bootstraps user space by assigning it a root capability to all available memory not used by the kernel. The initial user thread may split up the memory to create new, isolated applications. Thus, all new capabilities to subsets of the system's resources are derived from the root capability. The monotonic nature of capabilities ensures that no user space application has access to the kernel.

The capability-based access control also governs all seL4 kernel services. In order to perform any operation, an entity must invoke a capability with the respective access rights that it has in their possession. Capabilities always refer to a kernel object.

#### 2.3.2 Kernel objects

The kernel objects defined by seL4 form the interface to the kernel itself. An application that interacts with the kernel, does so via the creation, manipulation and combination of the kernel objects. We only describe a subset of object types that are most relevant to this work.

**Thread control blocks** represent a thread of execution that may be scheduled, blocked, or unblocked depending on its interaction with other threads. A thread control block has an associated CSpace and virtual address space (VSpace).

**Virtual address space objects** construct a VSpace for one or more threads, effectively creating a sandbox around applications. A VSpace consists of a memory paging structure of at least one level, depending on the specific hardware-level architecture. For example, the following objects in seL4 correspond to the two-level paging structure

of the Arm 32-bit ISA.

- 1. PageDirectory

- 2. PageTable

The lowest level of the paging structure will be filled with Frame objects that correspond to frames of physical memory.

**Endpoints** facilitate message passing communication between threads, but also between applications and the kernel itself. IPC uses Endpoints and is synchronous. Capabilities to Endpoints can be restricted to send- or receive-only. Communication requires two Endpoints; one per direction. Capabilities can be sent in a message over Endpoints to transfer them.

**Untyped** memory objects are the foundational unit of memory allocation in seL4. Untyped objects can be *retyped* into other kernel objects. Additionally, they can be divided into smaller groups such that part of the system's memory can be delegated.

#### 2.3.3 Memory allocation

The seL4 kernel does not dynamically allocate memory for kernel objects. Instead, applications must explicitly create objects by *retyping* Untyped kernel objects. The seL4 kernel provides system calls to retype Untyped objects. An application must have a sufficient capability to these Untyped objects in order to create new objects. These mechanisms for memory management enforce the isolation of physical memory between different applications.

Upon booting a system, the seL4 kernel sets up all memory. It first allocates the memory required for the kernel itself. seL4 then creates an initial user space thread to which it transfers all capabilities to the remaining Untyped memory, and a few capabilities to kernel objects necessary for bootstrapping the first thread. The kernel hands over control to the user space thread. The user space thread may split up the Untyped memory regions, create new threads or other kernel objects, and delegate authority to parts of the system as it sees fit.

#### 2.3.4 CAmkES and capDL

To make practical development on top of seL4 easier, there is the CAmkES software library and framework. CAmkES supports component-based development of full software systems with strong isolation guarantees [52][73]. It provides interfaces between components via remote procedure calls (RPCs) for synchronous communication based on seL4 Endpoint kernel objects. The two other communication interfaces are *Events* for notifications and *Dataports* for shared data buffers. Each CAmkES component is al-

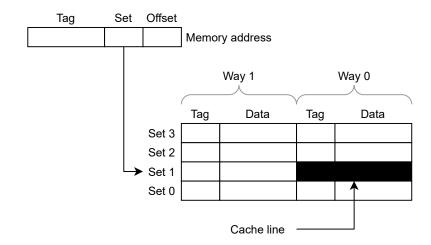

**Figure 2.3.** An example of an seL4 system and the capabilities and objects involved. There are two components: the Client and the Server. Their respective thread control blocks (TCBs) contain capabilities to the top levels of their VSpace and CSpace. Both components possess capabilities to two Endpoint objects (EP) used for synchronous inter-process communication (IPC). They also both map two Frame objects into their address space as shared memory for communication. The address space paging structure in this example is based on the implementation of Arm 32-bit ISA: page directory (PD), page table (PT), and their respective entries.

located a separate VSpace. This provides complete isolation between components, and only allows explicitly exposed, well-defined communication interfaces. A CAmkES application is defined using the architecture description language (ADL) that describes components, their assembly, connections, and configuration. The CAmkES framework processes all descriptions, combining it with code scaffolding, to build a complete and bootable seL4 system image.

The capability description language (capDL) provides a way to explicitly describe the capability distribution in seL4 systems [53, 74], i.e., a mapping between subjects and object capabilities. SeL4 can use a capDL specification during its bootstrapping process to simplify initialization of the system. CAmkES does this by default.

The seL4 project includes proofs that seL4 correctly initializes a system from boot state into a defined protection state described by a capDL specification [76].

A capDL specification consists of two sections: objects, and capabilities. The objects section describes all seL4 kernel objects in the system. The capabilities section specifies the capabilities that every component in the system is assigned. Figure 2.3 presents an example of a system with a client and a server component that communicate via two endpoints and two shared frames. Listings 2.4 and 2.5 contain the corresponding capDL specification.

```

objects {

2

client_tcb = tcb

3

client\_cnode = cnode

4

client_pd = pd

5

client_pt = pt

6

frame_client_0000 = frame(4k, fill: [file, offset])

7

frame_client_0001 = frame(4k, fill: [file, offset])

8

9

server_tcb = tcb

10

server_cnode = cnode

11

server_pd = pd

12

server_pt = pt

13

frame_server_0000 = frame(4k, fill: [file, offset])

14

frame_server_0001 = frame(4k, fill: [file, offset])

15

16

example_endpoint_0 = ep

17

example_endpoint_1 = ep

18

19

shared_frame_0 = frame (4k, fill: [])

20

shared_frame_1 = frame (4k, fill: [])

21

```

**Figure 2.4.** The objects section of a capability description language (capDL) specification for the example system; simplified. The declaration of thread control block (TCB) objects on lines (2) and (9) will create the respective applications in the seL4 system. Subsequent lines declare the virtual address space (VSpace) and capability space (CSpace) objects. Both applications declare two frame objects (6-7) and (13-14) that are filled with their corresponding memory frames containing the application's executable. Lines (16-17) declare the Endpoint objects (EP) for communication between components. Lines (19-20) declare the shared Frame objects and keeps them empty.

```

caps {

2

client_tcb {

3

cspace: client_cnode

4

vspace: client_pd

5

6

7

client_cnode {

8

0x1: example_endpoint_0

9

0x2: example_endpoint_1

10

11

12

client_pd {

13

0x0: client_pt

14

15

16

client_pt {

17

0x0: frame_client_0000 (RWX)

18

0x10: frame_client_0001 (RWX)

19

0x20: shared_frame_0 (RWX)

20

0x30: shared_frame_1 (RWX)

21

22

23

-- server capabilities follow analogously --

24

```

Figure 2.5. The capabilities section of a capability description language (capDL) specification for the example system; simplified. Lines (2-5) initialize the thread control block (TCB) object with capabilities to the roots of the client's capability space (CSpace) and virtual address space (VSpace), which were defined in Listing 2.4. Lines (7-10) initialize the client's CSpace with capabilities to the two Endpoints (EP) in the system. Lines (17-18) map the application's executable in its VSpace with read-write-execute permissions. Lines (19-20) map the shared frames into the client's VSpace. The capability setup for the server component is similar to the client's, except that it uses its respective object names.

## 3. Problem statement

"The mystery of life isn't a problem to solve, but a reality to experience."

Frank Herbert, Dune

In this chapter we introduce the system and adversary models, in addition to the goals and requirements of our work. The system model provides a brief overview of the main components in the system and serves as context for the remainder of the chapter. The adversary model describes an adversary's goals and capabilities that in turn inform the requirements of a system. When evaluating a system, the achieved functionality and security are only meaningful in perspective of an adversary model. Finally, we formulate the goals and a set of concrete requirements to help evaluate our work.

#### 3.1 System model

The system on which we build consists of three main components.

- 1. A rich execution environment (REE)

- 2. A trusted execution environment (TEE)

- 3. A co-processor

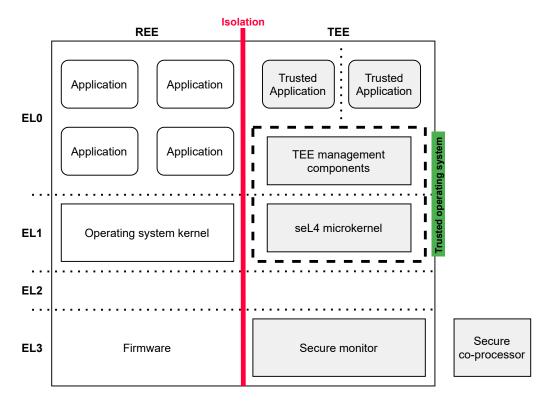

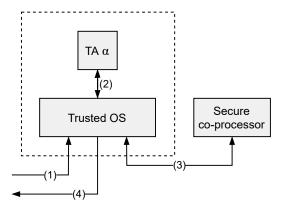

Figure 3.1 shows a simple system overview.

Firstly, the REE runs a general-purpose operating system (OS) — e.g. GNU/Linux — and any number of user space applications.

Secondly, the system has a separate TEE that runs a specialized, trusted OS. The system provides integrity guarantees between the REE and the TEE, such that the TEE can provide execution isolated from the REE. Applications from the REE can invoke functionality on the TEE and load their own trusted applications (TAs), but cannot directly manipulate memory or execution of the TEE.

Thirdly, the system contains a co-processor that is separated from the main processor. We assume there is a secure communication channel in place between the TEE and the co-processor. This co-processor performs sensitive cryptographic operations and stores cryptographic secrets. The manufacturer initializes the co-processor with a hardware root of trust (RoT).

The system has a hardware RoT that verifies the boot process of the firmware, which

**Figure 3.1.** A minimal overview of the system model. The system is split into a separate rich execution environment (REE) and trusted execution environment (TEE). Execution and memory are isolated between the REE and TEE, though both still operate on the same system on chip (SoC). The secure co-processor is a separate chip for cryptographic operations that communicates with the TEE on the main SoC.

then ensures that the TEE is initialized correctly and separately from the REE. This is similar to the operation of Arm TrustZone (Section 2.1.3).

#### 3.2 Adversary model

We consider an adversary with two goals: 1) forge attestation reports, and 2) execute unauthorized instructions in TAs. The adversary's first goal is to forge attestation reports to remote parties, in order to impersonate legitimate TAs. Consequently, the remote party might expose sensitive information when they continue communication with the adversary. The adversary's second goal is to compromise the integrity of a legitimate TA in order to alter its behavior.

We assume that the adversary controls the REE, including user space processes and the OS. Consequently, the adversary can load arbitrary TAs in our TEE. This means that the adversary can execute any malicious code in the TEE and attempt to forge TA-specific attestations. Lastly, we assume that the adversary is able to compromise confidentiality of the TEE's trusted OS and TAs. They would achieve this either by exploiting bugs in the trusted OS or TA code, or by leveraging side-channel attacks (Section 2.2).

However, we assume that the hardware is secure and uncompromised, and that the attacker cannot physically tamper with the hardware. Only a small fraction of real-world attackers will have the resources to tamper with the physical SoC of a target, thus we deem this a modest claim.

We assume that the secure co-processor guarantees confidentiality of its data and operations. This is a reasonable assumption, as there already exist secure elements that fit this claim — e.g., Apple's Secure Enclave [5], Google's Titan M [86], and the OpenTitan project<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>https://opentitan.org/

In summary, the assumptions that form our adversary model are as follows.

- The adversary has full control over the REE and can thus load and execute arbitrary TAs.

- The adversary can compromise confidentiality of TAs and the TEE OS.

- The adversary is unable to physically compromise the main processor or the co-processor.

- The adversary is unable to break confidentiality of the co-processor.

#### 3.3 Goals and requirements

The motivation for this thesis work is to design an architecture for TEE remote attestation that guarantees integrity in the presence of an adversary as described in Section 3.2. The TEE must provide remote attestation of TAs, even when confidentiality of the TEE and TAs cannot be guaranteed. It must also guarantee integrity of other TAs and the TEE in the presence of a TA loaded and controlled by the adversary. Additionally, the TEE must support the secure dynamic loading of a new TA during run-time. We desire a relying party to be able to perform secure remote attestation and trust that the attested software is executed.

Our security requirements are thus as follows.

- S-1: Provide secure remote attestation even when confidentiality of the TEE and TAs cannot be guaranteed.

- S-2: Retain isolation and integrity guarantees of TAs and the TEE, even in the presence of an adversary-controlled TA.

- S-3: Support secure dynamic loading of TAs.

Finally, we formulate a performance requirement for the attestation process of TAs.

P-1: The performance for attestation of TAs should be affordable relative to the full execution cost of a TA.

# 4. Design

"How do you cause people to believe in an imagined order such as Christianity, democracy or capitalism? First, you never admit that the order is imagined."

Yuval Noah Harari, Sapiens

#### 4.1 High-level system design overview

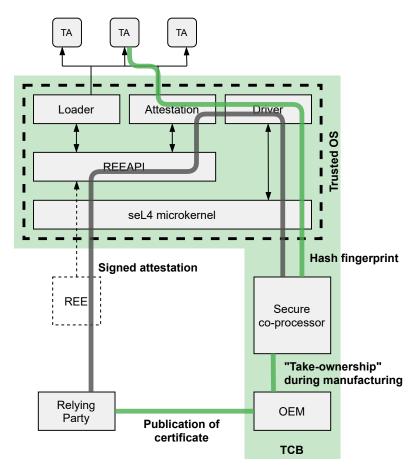

Figure 4.1 shows the high-level system overview. Our design leverages the co-processor and the formally verified seL4 microkernel to achieve security properties neither provide on their own. We use seL4 as a basis for the trusted operating system (OS) of the trusted execution environment (TEE). We chose the seL4 microkernel because of its formally verified implementational correctness and formal model guaranteeing confidentiality and integrity (S-2). These properties provide strong isolation between all the components of our trusted OS design. The trusted OS manages the trusted applications (TAs) that will be executed in the TEE. Thus, the TAs will have the same isolation guarantees with respect to the TEE and other TAs.

However, seL4 does not formally prove protection against timing-based side-channel attacks. Though it provides mitigations for specific attacks — e.g., speculative execution attacks such as Spectre and Meltdown (Section 2.2.3) — it does not rule out the whole class of attacks. This is problematic when performing remote attestation, because it means that the confidentiality of cryptographic keys used to sign the attestation reports is not ensured. Previous work showed how the compromise of similar secrets lead to the breach of integrity in Intel's Software Guard Exentsions (SGX) enclaves that performed the attestation reporting (Section 2.2.3). An adversary can then forge attestation reports of TAs. To address this, our design relies on the secure co-processor to manage confidential data such as cryptographic secrets, and to perform sensitive cryptographic operations. This prevents the compromise of these cryptographic secrets and thus ensures integrity and confidentiality of the attestation procedure, addressing requirement S-1.

In our design we distinguish between a rich execution environment (REE) or non-secure world, and a TEE or secure world. This is derived from the split-world architecture of Arm TrustZone (Section 2.1.3).

**Figure 4.1.** System architecture design with a rich execution environment (REE) and a trusted execution environment (TEE). The TEE runs a trusted operating system (OS) consisting of the seL4 microkernel and several management components. The trusted OS hosts every trusted application (TA) as an isolated component in itself. The confidentiality of the TEE maybe be compromised by side-channel attacks. Therefore, security critical data and operations are offloaded to the secure coprocessor in the design.

## 4.2 Trusted OS design

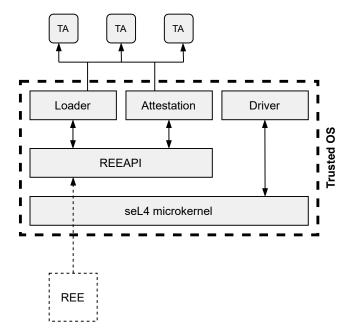

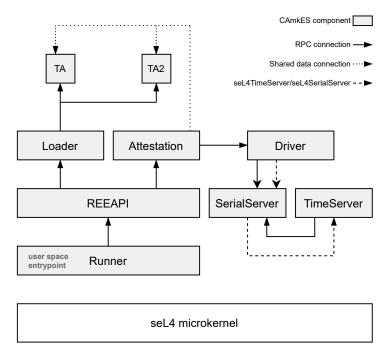

The trusted OS of the TEE consists of the seL4 microkernel and multiple CAmkES components. Figure 4.2 shows an overview. There are four components that provide the TEE functionality: REEAPI, Loader, Attestation, and Driver.

**REEAPI** provides an application programming interface (API) to the REE for managing the TEE and TAs. It exposes three methods: 1) loading a TA, 2) attesting a TA, and 3) calling exposed TA functionality. To coordinate loading and attesting TAs, the REEAPI shares a remote procedure call (RPC) communication channel with the respective components implementing these functions in the TEE. However, the REEAPI cannot call functions exposed by a TA directly, because of seL4's strict isolation. All RPCs must be explicitly defined at build time. Thus, the REEAPI calls the Loader via a pre-defined RPC channel, with the function to be called as an argument.

**Loader** prepares a memory area for TAs to be loaded and initializes them into place. During run-time, the REEAPI may receive a request to load a specific TA into the TEE. Internally, it forwards this request to the Loader component. A TA is an executable and linkable format (ELF) binary file that is the product of a compilation process for

the TEE platform. The Loader receives a TA ELF file via a shared buffer with the REEAPI and correctly loads it into the prepared memory area such that its exposed functionality can be called, addressing requirement **S-3**. In the special case that a TA is already statically defined during the build process of the system, the Loader is not required to perform its normal operation anymore.